課題解決事例

FPGAによる正確性向上

お客様の要望・課題

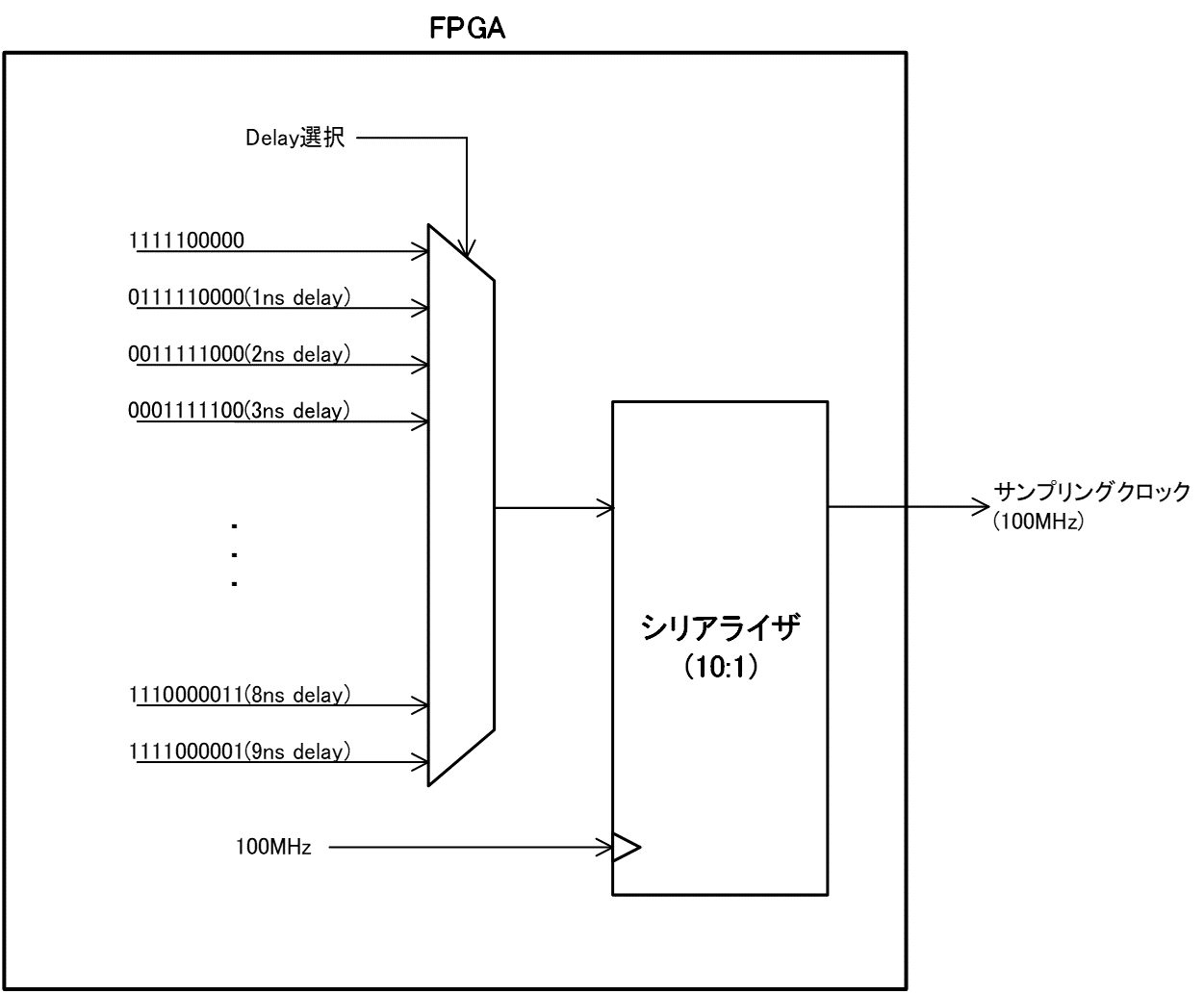

ADCのサンプリング位置を1ns±1nsステップで設定したいといった要望がございました。しかしながら、 Delayライン等を使用するとサンプリング位置のばらつきが大きくなってしまいます。

提案内容・効果

FPGAのOSERDESEを使用することで、お客様の要望であったステップ時間(1ns)のばらつきの低減を実現しました。 (クロックジッタ程度)さらにサンプリング周波数やステップ時間の可変化が可能になりました。

ポイント